- 您现在的位置:买卖IC网 > Sheet目录368 > UPD44647366AF5-E22-FQ1-A (Renesas Electronics America)SRAM QDRII 72MBIT 165-PBGA

�� �

�

�

�μ� PD44647094A-A,� 44647184A-A,� 44647364A-A,� 44647096A-A,� 44647186A-A,� 44647366A-A�

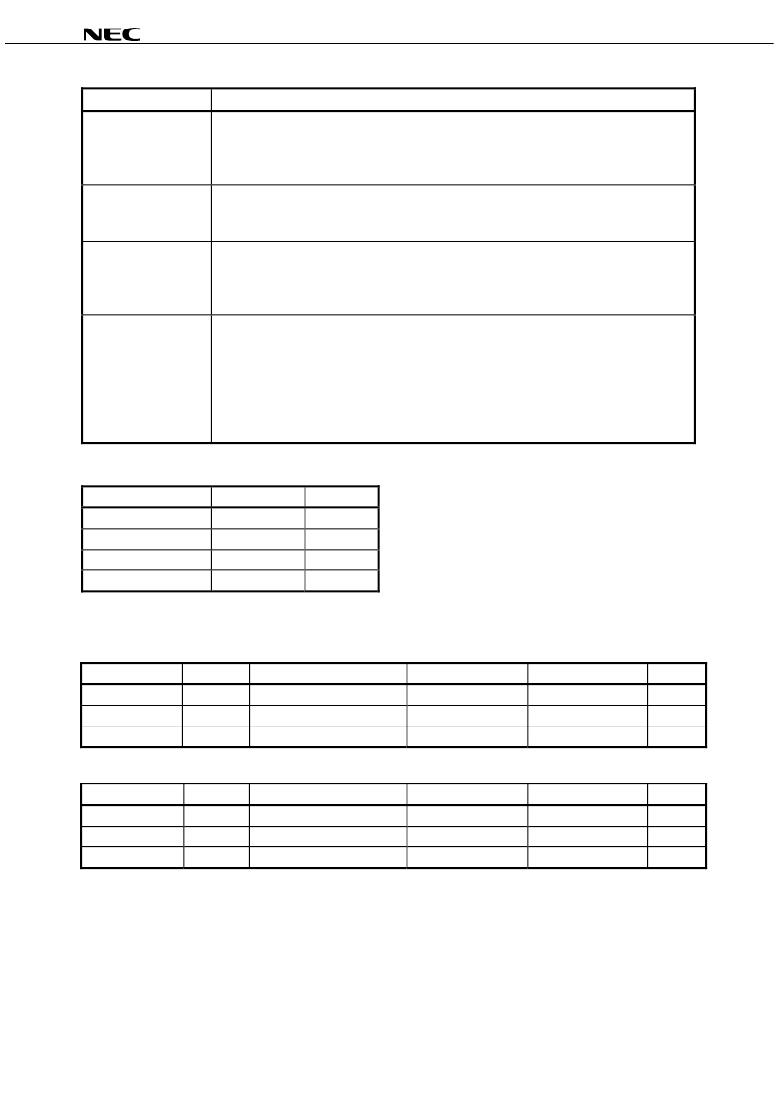

�Scan� Register� Definition� (1)�

�Register� name�

�Instruction� register�

�Bypass� register�

�ID� register�

�Boundary� register�

�Description�

�The� instruction� register� holds� the� instructions� that� are� executed� by� the� TAP� controller� when� it� is�

�moved� into� the� run-test/idle� or� the� various� data� register� state.� The� register� can� be� loaded� when� it� is�

�placed� between� the� TDI� and� TDO� pins.� The� instruction� register� is� automatically� preloaded� with� the�

�IDCODE� instruction� at� power-up� whenever� the� controller� is� placed� in� test-logic-reset� state.�

�The� bypass� register� is� a� single� bit� register� that� can� be� placed� between� TDI� and� TDO.� It� allows� serial�

�test� data� to� be� passed� through� the� RAMs� TAP� to� another� device� in� the� scan� chain� with� as� little� delay�

�as� possible.�

�The� ID� Register� is� a� 32� bit� register� that� is� loaded� with� a� device� and� vendor� specific� 32� bit� code� when�

�the� controller� is� put� in� capture-DR� state� with� the� IDCODE� command� loaded� in� the� instruction� register.�

�The� register� is� then� placed� between� the� TDI� and� TDO� pins� when� the� controller� is� moved� into� shift-DR�

�state.�

�The� boundary� register,� under� the� control� of� the� TAP� controller,� is� loaded� with� the� contents� of� the�

�RAMs� I/O� ring� when� the� controller� is� in� capture-DR� state� and� then� is� placed� between� the� TDI� and�

�TDO� pins� when� the� controller� is� moved� to� shift-DR� state.� Several� TAP� instructions� can� be� used� to�

�activate� the� boundary� register.�

�The� Scan� Exit� Order� tables� describe� which� device� bump� connects� to� each� boundary� register�

�location.� The� first� column� defines� the� bit’s� position� in� the� boundary� register.� The� second� column� is�

�the� name� of� the� input� or� I/O� at� the� bump� and� the� third� column� is� the� bump� number.�

�Scan� Register� Definition� (2)�

�Register� name�

�Instruction� register�

�Bypass� register�

�ID� register�

�Boundary� register�

�Bit� size�

�3�

�1�

�32�

�109�

�Unit�

�bit�

�bit�

�bit�

�bit�

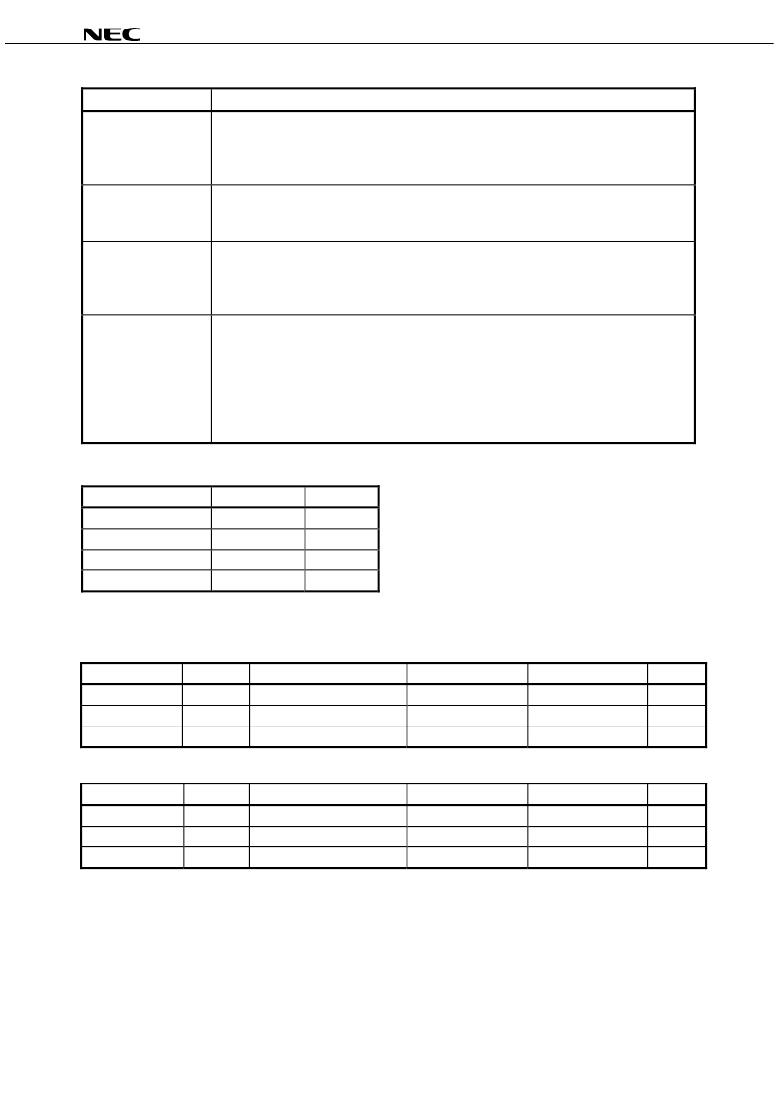

�ID� Register� Definition�

�2.0� Clock� Cycles� Read� Latency�

�Part� number�

�μ� PD44647094A-A�

�μ� PD44647184A-A�

�μ� PD44647364A-A�

�Organization�

�8M� x� 9�

�4M� x� 18�

�2M� x� 36�

�ID� [31:28]� vendor� revision� no.�

�XXXX�

�XXXX�

�XXXX�

�ID� [27:12]� part� no.�

�0000� 0000� 1001� 0101�

�0000� 0000� 1001� 0110�

�0000� 0000� 1001� 0111�

�ID� [11:1]� vendor� ID� no.�

�00000010000�

�00000010000�

�00000010000�

�ID� [0]� fix� bit�

�1�

�1�

�1�

�2.5� Clock� Cycles� Read� Latency�

�Part� number�

�μ� PD44647096A-A�

�μ� PD44647186A-A�

�μ� PD44647366A-A�

�Organization�

�8M� x� 9�

�4M� x� 18�

�2M� x� 36�

�ID� [31:28]� vendor� revision� no.�

�XXXX�

�XXXX�

�XXXX�

�ID� [27:12]� part� no.�

�0000� 0000� 1010� 0001�

�0000� 0000� 1010� 0010�

�0000� 0000� 1010� 0011�

�ID� [11:1]� vendor� ID� no.�

�00000010000�

�00000010000�

�00000010000�

�ID� [0]� fix� bit�

�1�

�1�

�1�

�26�

�Data� Sheet� M19962EJ2V0DS�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

USB-100

KIT STARTER FOR USB

USBMLCF

USB BDM INTERFACE MC P&E

USBMLPPCBDM

MULTILINK P&E POWERPC USB

V-9767-L

DOOR ECONOGLAS 19" LOCKING

VC-9931

CABINT VISNCB 20.54X23.62X23.62"

VC-9934B

VISIONCAB B 35.40X23.62X23.62"

VLA500-01

IC IGBT GATE DVR/DC-DC CONV 12A

VLA502-01

IC IGBT GATE DVR/DC-DC CONV 12A

相关代理商/技术参数

UPD44647366AF5-E25-FQ1

功能描述:SRAM QDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)

UPD44647366AF5-E25-FQ1-A

功能描述:SRAM QDRII 72MBIT 165-PBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:3,000 系列:- 格式 - 存储器:EEPROMs - 串行 存储器类型:EEPROM 存储容量:8K (1K x 8) 速度:400kHz 接口:I²C,2 线串口 电源电压:1.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SOIC 包装:带卷 (TR)

UPD446C-2L

制造商:NEC Electronics Corporation 功能描述:2K X 8 STANDARD SRAM, 200 ns, PDIP24

UPD446G-20L

制造商:NEC Electronics Corporation 功能描述:2K X 8 STANDARD SRAM, 200 ns, PDFP24

UPD45128163G5

制造商:Renesas Electronics Corporation 功能描述:128 MBIT SDRAM

UPD45128163G5-A75-9JF

制造商:Elpida Memory Inc 功能描述:8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54

UPD45128841G5-A75-9JF

制造商:NEC Electronics Corporation 功能描述:SDRAM, 16M x 8, 54 Pin, Plastic, TSOP

UPD4516161AG5A109NF

制造商:NEC Electronics Corporation 功能描述: